12685 INTEL DRIVER

| Uploader: | Daishakar |

| Date Added: | 14 August 2004 |

| File Size: | 18.48 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 85582 |

| Price: | Free* [*Free Regsitration Required] |

Single-precision bit matrix input value. Clock input to the megafunction. This port enables division.

Floating-Point IP Cores User Guide

Asserted when the result of the inversion after rounding is a denormalized number. When this signal is low, no division takes place and the outputs remain the same.

Denormal numbers are forced-zero values, therefore, the inverse of a zero results in infinity. Super Pi Mod 1. The triangular matrix inversion process then generates the inverse of the lower triangular using backward substitution.

ALTERA_FP_MATRIX_INV IP Core

Choose the frequency in MHz at which this core is expected to run. You can customize the IP cores by configuring various parameters to accommodate your needs. The core resets asynchronously when the reset signal is asserted.

This design example produces a floating-point absolute value function for the multiplication results of single-precision format numbers. Conversion functions for the following formats: Specifies the rounding mode. Matrix A Avalon streaming valid signal.

The supported dimensions are 4 x 4, 6 x 6, 8 x 8, 16 x 16, 32 x 32, and 64 x As for the root section, the structure is simplified by the nature of the positive definite matrix.

The input data may be loaded at any time the ready signal is asserted even when the previously loaded data is still being computed.

Supports conversion of floating-point numbers in single, double, and single-extended precision formats. The single-extended precision format contains the following binary patterns: Output port for the multiplier. Cinebench R10 - Rendering Single 32Bit.

Clock input to the IP core. Compares and output the smallest value of two input.

Title for Topic

Matrices load row by row. All values seen on the output port before the 20th clock cycle are merely due to the behavior of the system during start-up and should be disregarded. Denormal inputs are not supported and are forced to zero before conversion takes place. Asserted when an invalid square root occurs, such as negative numbers or NaN inputs.

Floating-point numbers Special values zero, infinity, denormal numbers, and NaN bit combinations Single-precision, double-precision, and single-extended precision formats for floating-point numbers. The signal goes high when the exponent of the input x is smaller than LSBA.

This design example implements a floating-point multiplier for the multiplication of double-precision format numbers. As there are memory blocks already available for the storage of the input matrices in the Cholesky decomposition function, the memory blocks in the matrix multiplier are redundant and can be removed.

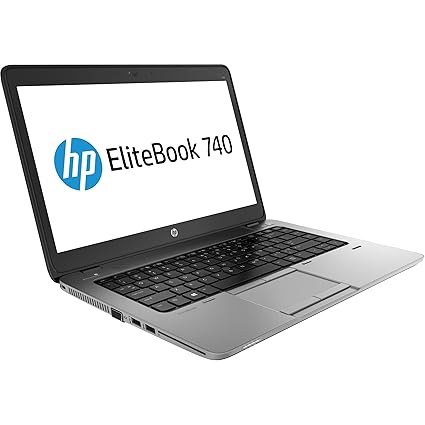

Intel Core i5-8250U

The output latency is 6, hence every division generates the output result 6 clock cycles later. In this case, a NaN value is output to the result[] output port. Asserted when the result of the addition or subtraction, after rounding, the value is zero and the inputs are not equal.

The diagonal value, which is the first value at the top of each column in the decomposition, is always a real number so that the result from the inverse square root calculation is always a real number.

Comments

Post a Comment